Search Results for author: Qiuwen Lou

Found 6 papers, 0 papers with code

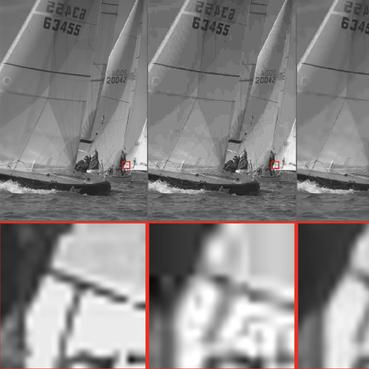

Super Efficient Neural Network for Compression Artifacts Reduction and Super Resolution

no code implementations • 26 Jan 2024 • Wen Ma, Qiuwen Lou, Arman Kazemi, Julian Faraone, Tariq Afzal

Video quality can suffer from limited internet speed while being streamed by users.

Device-Circuit-Architecture Co-Exploration for Computing-in-Memory Neural Accelerators

no code implementations • 31 Oct 2019 • Weiwen Jiang, Qiuwen Lou, Zheyu Yan, Lei Yang, Jingtong Hu, Xiaobo Sharon Hu, Yiyu Shi

In this paper, we are the first to bring the computing-in-memory architecture, which can easily transcend the memory wall, to interplay with the neural architecture search, aiming to find the most efficient neural architectures with high network accuracy and maximized hardware efficiency.

Nonvolatile Spintronic Memory Cells for Neural Networks

no code implementations • 29 May 2019 • Andrew W. Stephan, Qiuwen Lou, Michael Niemier, X. Sharon Hu, Steven J. Koester

A new spintronic nonvolatile memory cell analogous to 1T DRAM with non-destructive read is proposed.

Application-level Studies of Cellular Neural Network-based Hardware Accelerators

no code implementations • 28 Feb 2019 • Qiuwen Lou, Indranil Palit, Tang Li, Andras Horvath, Michael Niemier, X. Sharon Hu

While it is well-known that CeNNs can be well-suited for spatio-temporal information processing, few (if any) studies have quantified the energy/delay/accuracy of a CeNN-friendly algorithm and compared the CeNN-based approach to the best von Neumann algorithm at the application level.

A mixed signal architecture for convolutional neural networks

no code implementations • 30 Oct 2018 • Qiuwen Lou, Chenyun Pan, John McGuiness, Andras Horvath, Azad Naeemi, Michael Niemier, X. Sharon Hu

Deep neural network (DNN) accelerators with improved energy and delay are desirable for meeting the requirements of hardware targeted for IoT and edge computing systems.

Design Flow of Accelerating Hybrid Extremely Low Bit-width Neural Network in Embedded FPGA

no code implementations • 31 Jul 2018 • Junsong Wang, Qiuwen Lou, Xiaofan Zhang, Chao Zhu, Yonghua Lin, Deming Chen

To create such accelerators, we propose a design flow for accelerating the extremely low bit-width neural network (ELB-NN) in embedded FPGAs with hybrid quantization schemes.